# RAPPORT DE STAGE D'OPTION SCIENTIFIQUE

# $\frac{A\ Component\ Library\ for\ the}{Simulation\ of\ Chip\ Multiprocessors}$

MicroLib: une approche modulaire de la simulation de processeurs

# NON CONFIDENTIEL

Option: INFORMATIQUE

<u>Champ de l'option</u>: Architecture des ordinateurs

<u>Directeur de l'option</u>: Monsieur DOWEK, Gilles

<u>Directeur de stage</u>: Monsieur TEMAM, Olivier

Dates du stage : April 11 - Juillet 31

Adresse de l'organisme : INRIA Futurs

Parc Club Orsay Université,

ZAC des vignes

4rue Jacques Monod - Bât G91893 Orsay Cedex FRANCE

#### Abstract

Processor simulation is a key tool used in microprocessor research to evaluate the performance and usefulness of new ideas. Currently used simulators such as SimpleScalar are monolithic and optimized for superscalar processors. In the meantime the trend in research and Industry has gone to Chip Multiprocessors (CMP) and especially researchers want to focus on implementations with hundreds of cores. Unfortunately, the monolithic simulators fail to provide the needed compatibility to simulate CMPs. Newer modular solutions provide this compatibility, but they have not yet been used for in this way. Thus the needed CMP modules are missing. The main goal of my intership was the development of such a library. I have researched different existing solutions for CMPs and the Networks on Chip (NoC) connecting the CMP cores. From this information I have decided which modules are needed. Afterwards I have implemented and tested those modules. The second part of my intership was to investigate solutions for the interfacing of modules from different simulation environments. This will further help to facilitate module reuse and simulator construction in general. I have investigated two solutions to this problem. One I have developed and tested myself. The other I have started to work on recently and I have had already possitive results. The library I have developed will help researchers to test their CMP programs and construct a big number of different topologies. Our hopes are that this library will grow due to contributions by others a possibly become a standard toolkit for CMP simulation.

#### Résumé

La simulation des processeurs est la démarche principale utilisée dans la recherche d'architecture des ordinateurs. Les simulateurs actuellement utilisés, comme SimpleScalar, sont construits d'une manière monolithique et optimisés pour la simulation des processeurs superscalaires. Mais la dernière tendance dans la recherche et l'industrie est d'évoluer vers des multi-processeurs sur chip (chip multiprocessors -CMP). En particulier, les chercheurs veulent se focaliser sur des implémentations avec des centaines de noyaux. Cependant les simulateurs monolithiques ne parviennent pas à offrir la comptabilité nécessaire pour simuler des CMP. Des nouvelles solutions modulaires offrent cette possibilité mais malheureusement elles n'étaient pas encore utiliser de cette façon. Donc les modules nécessaires ne sont pas encore implémentés. Le but général de mon stage était de développer une telle bibliothèque. J'ai recherché des solutions existantes de CMP et de réseaux sur chip (network on chip - NoC) qui associent les noyaux des CMP. A partir de cette information, j'ai choisi les modules qui doivent nécessairement être réalisés. Ensuite, j'ai implémenté et testé ces modules. La seconde partie de mon stage à consisté à explorer les solutions possibles de pour la communication des modules provenant d'environnements de simulation différents. Cela peut faciliter la réutilisation des modules et la construction de simulateurs en général. J'ai envisagé deux solutions pour ce problème. J'ai déjà développé et testé la première. J'ai commencé à travailler sur la deuxième et j'ai déjà eu des résultats positifs. La bibliothèque que j'ai développé va aider d'autres chercheurs à tester leurs programmes pour CMP et à construire une quantité déjà considérable de topologies différentes. Nous espérons que cette bibliothèque va s'agrandir grâce à des contribution faites par d'autres équipes de recherche et peut-être devenir un outil standard pour la simulation CMP.

# Acknowledgments

First of all I would like to thank the whole Alchemy research group for the kindness and helpfulness they have offered me. I have really enjoyed my internship and a big part of this is due to the friendly atmosphere here.

I want to thank Prof. Temam for having let me work with his research team and bother them with questions. Also I want to thank him for all the useful comments and advises he gave me regarding this report and for all the other things he has helped me with.

I want to especially thank Daniel Gracia Pérez, Pierre Palatin, Yves Lhuillier, and Gilles Mouchard for having answered all my questions so patiently and for all the usefull comments and remarks they made regarding all aspects of my work.

Another special thanks goes to Sylvain Girbal and Pierre Palatin for having shown me all those linux tricks and having so often fixed some kind of problem with my account.

Orsay, June 29th, time: 31:14<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>There is no mistake here.

# Contents

| 1 | Intr | roduction                                              | 6         |

|---|------|--------------------------------------------------------|-----------|

| 2 | The  | e simulation environments                              | 8         |

|   | 2.1  | SystemC                                                | 10        |

|   | 2.2  | MicroLib                                               | 15        |

|   | 2.3  | Liberty                                                | 17        |

|   | 2.4  | SimpleScalar                                           | 20        |

| 3 | Des  | sign choices                                           | 21        |

|   | 3.1  | Existing CMP architectures and interconnects           | 21        |

|   |      | 3.1.1 A shared bus solution: Stanford Hydra CMP        | 21        |

|   |      | 3.1.2 Packet-switched networks: MIT RAW Microprocessor | 23        |

|   |      | 3.1.3 A ring bus: Cell Processor                       | 25        |

|   |      | 3.1.4 A crossbar interconnect                          | 27        |

|   |      | 3.1.5 SPIN                                             | 28        |

|   | 3.2  | Selecting a Network on Chip for CMP                    | 30        |

|   | 3.3  | Selecting a core for CMP                               | 31        |

|   | 3.4  | Selecting a memory                                     | 32        |

| 4 | Imp  | plementation of the modules                            | 33        |

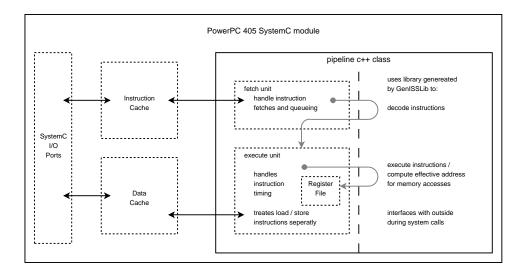

|   | 4.1  | The PowerPC 405 processor module                       | 33        |

|   |      | 4.1.1 Problems encountered                             | 33        |

|   |      | 4.1.2 Hardware architecture                            | 34        |

|   |      | 4.1.3 Instruction Set Architecture                     | 36        |

|   |      | 4.1.4 Implementation                                   | 36        |

|   |      | 4.1.5 Verification with an emulator                    | 39        |

|   | 4.2  | The Network on Chip module                             | 40        |

|   |      | 4.2.1 Architecture                                     | 40        |

|   |      | 4.2.2 Implementation                                   | 41        |

|   |      | 4.2.3 Possible improvements                            | 43        |

|   | 4.3  | The memory module                                      | 43        |

| 5 | Cor  | nmunication between different simulation environments  | 44        |

|   | 5.1  | A common communication channel                         | 46        |

|   |      | 5.1.1 Socket-based communication                       | 46        |

|   |      | 5.1.2 Implementation                                   | 48        |

|   |      | 5.1.3 Performance                                      | 49        |

|   | 5.2  | An LSS wrapper                                         | 49        |

| 6 | Sim  | ulation                                                | <b>52</b> |

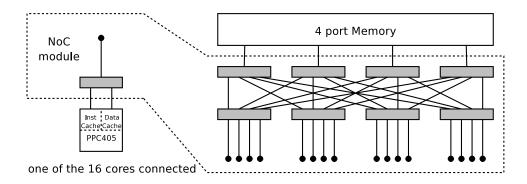

|   | 6.1  | A 16 core network on chip simulator                    | 52        |

|   | 6.2  | Simulation using sockets                               | 54        |

| 7            | Future work 55                   |           |  |  |  |

|--------------|----------------------------------|-----------|--|--|--|

| 8            | Personal conclusion              | 57        |  |  |  |

| A            | FastSysC                         | <b>58</b> |  |  |  |

| В            | A simple test program            | 60        |  |  |  |

| $\mathbf{C}$ | A LFSR implementation in SystemC | 61        |  |  |  |

|              | C.1 xor.h                        | 61        |  |  |  |

|              | C.2 flipflop.h                   | 61        |  |  |  |

|              | C.3 tee.h                        | 62        |  |  |  |

|              | C.4 lfsr.h                       | 62        |  |  |  |

|              | C.5 main.cpp                     | 63        |  |  |  |

| D            | A LFSR implementation in LSE     | 65        |  |  |  |

|              | D.1 xor_gate.lss                 | 65        |  |  |  |

|              | D.2 lfsr.lss                     | 65        |  |  |  |

# 1 Introduction

The simulation of processor architectures is the core tool used by microarchitecture researchers for the purpose of evaluating the performance and usefulness of new ideas [6]. Most research papers on computer architecture include performance measurements that have been determined by simulation [5]. These simulations range from bit-accurate simulations on the gate level to functional simulations for testing program behavior for example.

The most commonly used simulation tool for this purpose is SimpleScalar [14]. More than 50% of the articles published on computer architecture use it to test their research ideas [39, 45]. SimpleScalar is a tool suit that contains multiple simulation source codes that can be adapted by researchers to suit their needs. It has been developed for the simulation of superscalar processors and is preferably used for out-of-order processor architectures. Research on this type of processors has been highly fruitful. As technology allowed us to fit more and more transistors on a single silicon chip and clock them at higher frequencies the superscalar processors consumed the resources given producing in turn bigger pipelines and wider instruction windows that allowed for ever faster execution and data throughput. Throughout this time SimpleScalar has served as an irreplaceable tool to the developers.

But the situation is currently changing. While today's technology allows us to fit more than a billion transistors on a single silicon chip the huge processors cannot cope anymore with the increasing frequencies due to signal runtimes on the chip. In today's modern processors an electric pulse that runs across the die needs multiple clock-cycles to actually cross it [28]. This effect worsens as frequency increases. Intel has officially announced that it has problems reaching the 4.0 GHz frequency with its processors. And although the new Cell Processor is going to be able to run at 4.6 GHz [26] a current trend towards another solution can be observed. Developers are stopping to increasing the frequency and utilize the transistor budget for area expensive predictions units to accommodate for worsening pipeline effects. Instead the industry has started to invest transistor resources into multiple processor cores on a single chip. Already Intel has produced a dual core Itanium 2 processor with 1.7 billion transistors [24, 25, 21]. IBM also has a dual core processor on his range of products: The Power4 [41]. This new evolution has even led to stripping down the processor cores in order to be able to place more of them on a single die. As an example an eight in-order core solution in the form of the Cell Processor [44, 26] is on its way to the global market. And processor dies with as many as 16 in-order cores have already been implemented by researchers as in the case of the MIT Raw Microprocessor [9]. These new types of processors are called *chip* multiprocessors (CMP).

Unfortunately SimpleScalar fails to provide adequate service for this new research branch. At the time SimpleScalar was designed the world focused

on superscalar processors and multiprocessors were not on debate. Thus the simulator lacks the ability for CMP simulation. A strong handicap that actually prevents SimpleScalar from effectively evolving in this way is the fact that it is based on a monolithic design. The whole simulator is encapsulated as one big program code and thus changes are hard to make. New simulation environments such as SystemC [1] and Liberty [13] have brought a promising solution to the problem. They are based on modules and thus offer a far bigger flexibility than SimpleScalar. Sadly these environments have so far not been used to provide appropriate CMP simulation support. Instead most module libraries published for these environments focus mainly on components needed for the simulation of superscalar processors. An example is MicroLib [5] that contains models like that of the PowerPC 750 processor [15] or a general superscalar processor module called OoOSysC [22]. These modules can be well branched together to form a multiprocessor simulator with a few cores. But they do not resemble the current research trend to use simpler cores in order to be able to have hundreds of them on a single chip.

These issues motivated the development of a new library specially designed for chip multiprocessor simulation. The first goal was to identify the components that would best fit in such a library. This included selecting currently used architectures and the correct granularity of the modules. Afterwards the chosen modules needed to be implemented. Major terms to be fulfilled were a very strong flexibility of the modules and the possibility for expansion. This will allow for better reuse by other research groups. Another very important objective was decent simulation speed of the modules. Reasearch always focuses on future products. Since there already are CMPs with a few cores on the market this means that researchers should start investigating architectures with hundreds of cores and more. Thus every waste of simulation time in a module will be multiplied by the number of hundreds of instantiations of this module. In order to receive significant results for a simulation researchers need to at least simulate a million instructions. If the modules proposed will not result in fast simulators they are of limited usability.

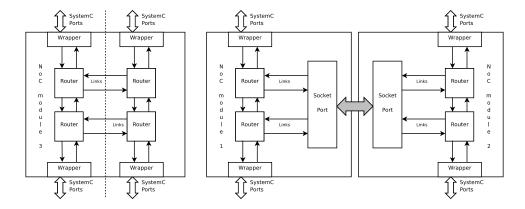

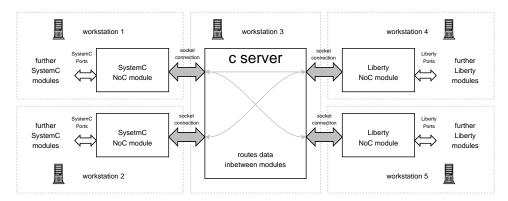

A second goal of this project addressed a related issue. As already mentioned two modular simulation environments are currently evolving as far more flexible tools than SimpleScalar: SystemC and Liberty. Unfortunately until now these environments are incompatible with each other. This means that so far modules written for SystemC cannot be used together with modules written for Liberty. Due to this circumstance reuse is strongly limited to one simulation environment. The Liberty Research Group [38] and the Alchemy Research Group [37, 5] have both expressed the need for a solution to this problem. Thus a second part of this project was to investigate possibilities to connect modules from these two environments.

While these goals might seem very clear it has to be pointed out that they are almost infinite. The library motivated above can easily contain hundreds of components. Since I had only little more than 3 months during this project my goal was to start up this library by creating the absolutely necessary modules for a working instance of a CMP simulator. I have tried to make these modules as adjustable as possible to already allow for effective recycling in other simulators. My choices regarding the modules have been guided by current research but also by the needs of the research group I work with, the Alchemy Group at INRIA Futurs. To some extend the fact that a cooperation with the Liberty Research Group at Princeton is planned for the future also influenced my decision.

The rest of the report is organized as follows. Section 2 describes the most commonly used simulation environments, two of which I have been working with. In Section 3 I give an introduction to the domain of Chip Multiprocessors by presenting existing solutions and then describe the design choices I have made. Section 4 talks about the actual implementation details of the modules chosen in Section 3. Interfacing possibilities of different simulation environments, including two possible solutions, are being discussed in Section 5. In Section 6 I demonstrate how to construct a simulator from the modules implemented. Finally Section 7 discusses future work to be done and Section 8 concludes the project experiences.

# 2 The simulation environments

In this section I will introduce the four simulation environments mentioned above: SystemC [1], MicroLib [5], Liberty [13], and SimpleScalar [14]. All three environments have been widely used in past and current research [16].

I have written all modules in SystemC since this way I was able to reuse existing tools developed by the research group which I have joined during this internship. Also SystemC allows for the most flexibility when developing modules. Thus it was the most important simulation environment for this project and I will present it first. Next I will present MicroLib, a modular simulation environment that is a continuation of SystemC. After that I will introduce the Liberty Simulation Environment (LSE). It is often just called Liberty after the research groups name that has developed it. Liberty has been important in the second part of this project when investigating interface possibilities between SystemC and LSE. At last I will shortly present SimpleScalar. I have not really worked with SimpleScalar and it does not very well suit my purpose since it is not module based. Still I feel that it is worth mentioning due to its widespread use in the computer architecture research community [39].

For a quick overview of all simulation environment please refer to Table 1.

| Name         |                                          | Properties                                                     |  |

|--------------|------------------------------------------|----------------------------------------------------------------|--|

| SystemC      | +                                        | - Highly modular simulation environment.                       |  |

|              | +                                        | Implemented as a c++ library.                                  |  |

|              | +                                        | Leaves huge freedom to the user in defining modules and        |  |

|              |                                          | communication interfaces.                                      |  |

|              | +                                        | User has control of the main routine.                          |  |

|              | _                                        | Communication between modules via ports is slow.               |  |

| MicroLib     | +                                        | Highly modular simulation library for processors.              |  |

|              | +                                        | Common interfacing standards.                                  |  |

|              | +                                        | Many modules that can be branched together.                    |  |

|              | +                                        | Wrappers for other simulation environments.                    |  |

| Liberty      | + Highly modular simulation environment. |                                                                |  |

|              | +                                        | Defines its own API and syntax.                                |  |

|              | +                                        | Generates c++ code and compiles it into simulator using g++.   |  |

|              | +                                        | Allows for strong optimization due to the fact that the model  |  |

|              |                                          | structure is known at compile time.                            |  |

|              | _                                        | Leaves not much freedom to the user concerning communi-        |  |

|              |                                          | cation between modules above the simulation level.             |  |

|              | _                                        | Only a handfull of data types. No possibility to pass classes  |  |

|              |                                          | as data like in SystemC.                                       |  |

|              | _                                        | Quite a hassle to install.                                     |  |

| SimpleScalar | +                                        | Widely used simulator for superscalar processors.              |  |

|              | +                                        | Implemented as parametrized c++ code.                          |  |

|              | -                                        | Impractical for simple processor cores like those used in chip |  |

|              |                                          | multiprocessors.                                               |  |

Table 1: Different simulation environments

### 2.1 SystemC

SystemC is a class library implemented in standard C++. It provides hardware-oriented constructs that allow for low-level as well as high-level modeling of hardware architectures. It is supported by more than 50 companies from the System on Chip domain [45]. In the follwing I will only describe the parts of SystemC that have been usefull to me. Please note that a complete and exhaustive description of SystemC would go beyond the scope of this report and only bore the reader. I felt though, that basic knowledge about SystemC should be provided in order to allow to clearly understand this project.

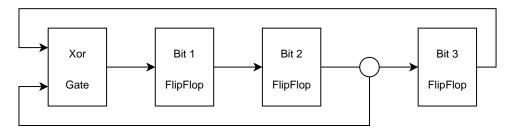

In SystemC a model might consist of modules with ports, clocks and signals. In the following I will describe these building parts while explaining how to implement a simple Linear Feedback Shift Register (LFSR). This is an standard example in simulation environment documentations since it is simple to understand and utilizes the most important parts of the simulation environment. I will first demonstrate the definition of a xor-gate and a flip-flop and latter combine those to a working 3-bit LFSR as can be seen in figure 1.

Figure 1: A simple three bit Linear Feedback Shift Register (LFSR).

Modules are the basic building blocks written in C++. A new module is declared like a new C++ class using the construct sc\_module. They describe basic structures like gate and Flip-Flops for detailed-level simulations or more complex structures like caches, memories and ALUs. In most processor or hardware system simulations more complex structures are implemented by modules. This increases facility of inspection and decreases development time. Also simulation speed is increased since each module is treated as a separate object during simulation and thus generates additional computation overhead. The declaration of our xor-gate will thus look like this:

```

sc_module XorGate {

...

}

```

To be able to communicate amongst each other, modules contain ports.

There are two groups of ports. Ports declared as sc\_in<type> serve as inputs to the module and are used to receive data of the type type. Ports declared as sc\_out<type> serve as outputs and are used to send data of the type type. Let us assume our xor-gate has two inputs and one output. To add these our declaration has to be changed to:

```

sc_module XorGate {

sc_in<boolean> op1, op2;

sc_out<boolean> res;

...

}

```

The module can now receive two boolean values, one on each of the ports op1 and op2. They can send their result by writting it to the port named res. In order to make our gate work we have to register it to the SystemC engine and create a SystemC processes that will compute the result. This is done in the constructor of our module:

```

sc_module XorGate {

sc_in<boolean> op1, op2;

sc_out<boolean> res;

XorGate() {

SC_MODULE();

HAS_PROCESS(ComputeResult);

sensitive << op1 << op2;

}

void ComputeResult() {

res = op1 ^ op2;

}

</pre>

```

First we have registered the module to the SystemC engine by calling SC\_MODULE(). Second we have registered a new process to the SystemC engine by calling HAS\_PROCESS(ComputeResult) and making it sensitive to both inputs. This means that the SystemC engine will call the method ComputeResult when one or both values of the inputs change. This method than computes the result of the operation and writes it to the outport. In SystemC most ports can be simply read and written like variables. The SystemC engine will automatically register changes to outports and react accordingly.

A process can be made sensitive to any number of inputs but not to outputs. It can also be made sensitive to the falling or rising edge of a clock

by writing sensitive\_pos « clk or sensitive\_neg « clk where clk is the name of the clock inport. A clock inport is declared using sc\_in\_clk. In our flip-flop we will make use of a clock. Additionally we need a variable to store the memorized value. Since SystemC modules are C++ classes they can contain any additional variables and methods as needed. Here the flip-flop code:

```

sc_module FlipFlop {

sc_in_clk clk;

sc_in<boolean> opin;

sc_out<boolean> opout;

boolean tmp;

FlipFlop() {

SC_MODULE();

HAS_PROCESS(DataIn);

sensitive << opin;

HAS_PROCESS(NewCycle);

sensitive_pos << clk;

}

void DataIn() {

tmp = opin;

void NewCycle() {

opout = tmp;

}

}

```

When a new value arrives at the input inop of our flipflop it will be memorised temporarily in the variable tmp. In the beginning of the next cycle the process NewCycle will write this temporary value to its output opout. In order to create our LFSR module we have to instantiate the correct number of flip-flops and a xor-gate and connect them. To create these connections in SystemC singals are used. Signal of the type type are declared using sc\_signal<type>. An outport of one module can be connected to an inport of the same or of a different modules by a signal. To do so, both ports as well as the signal need to be of the same data types. To connect outport with inport we write:

```

sc_signal<type> signalname;

outport(signalname);

inport(signalname);

```

This connection works different with clock inports. A clock inport is directly connected to another clock inport typing submodule->inClock(inClock). In the case of our LFSR its clock inport needs to be connected to the clock inports of the flip-flops. Thus the LFSR code will look like this this:

```

sc_module LSFR {

sc_in_clk clk;

FlipFlop *fp1;

FlipFlop *fp2;

FlipFlop *fp3;

XorGate *xor;

Tee<2>

*tee;

LFSR() {

fp1->clk(clk);

fp2->clk(clk);

fp3->clk(clk);

fp1->opin(xor_to_fp1);

fp1->opout(fp1_to_fp2);

fp2->opin(fp1_to_fp2);

fp2->opout(fp2_to_tee);

tee->opin(fp2_to_tee);

tee->opout[0](tee_to_fp3)

tee->opout[1](tee_to_xor)

fp3->opin(tee_to_fp3);

fp3->opout(fp3_to_xor);

xor->op1(tee_to_xor);

xor->op2(fp3_to_xor);

xor->res(xor_to_fp1);

}

}

```

The complete code of the LFSR can be seen in Appendix C. Note that there is a new module tee. It is needed to communicate the output of fp2 to

both fp3 and the xor gate xor because an outport can only be connected to one inport. The tee module simply writes the data it receives on its inport to all its outports. Notice that the class Tee<outnum> is templated and the number of outports is passed during declaration.

Finally we want to simulate our LFSR module. For this we have to create a method called sc\_main. It takes the same arguments as the main method of standard C++ programs, namely the command line parameters. When the simulator is compiled the internal main method of the SystemC library is used. When executed it calls the userdefined sc\_main method. This method has to instantiate the modules used for the simulation and signal the simulation engine to start.

Before we can run the simulation we have to declare a clock. This is done using the construct sc\_clock. We than instantiate the LFSR module and connect the clock to it by simply writing lfsr->clk(clock). The simulation needs then to be initialize and started for n clock cycles as follows:

```

sc_initialize();

sc_start(n);

```

When done simulating the first n cycles the method sc\_start returns. It can be re-executed to continue simulation form where it stopped. SystemC is not able to rewind in simulation or simulate backwards due to the complexity it offers.

Since the whole description of the modules is completely done in C++ counting variables, file input/output and so on can be added to the simulator in order to measure and see the effects of the simulation. This is one of the big advantages of SystemC that all powerfull tools given to the user by C++ can be reused in defining simulator modules. The whole text of the LFSR simulator can be found in Appendix C. Output is already contained in this code.

I have just described the general structure by which SystemC modules are defined and combined into more complex modules and finally into an executable simulator. It is of further interest to know a little bit about the simulation engine of SystemC. In fact, simulation in SystemC is event driven. This means that calculation processes in modules are started if certain events arrive. Such an event might be the rising edge of a clock or changed data on one of the input ports. When a clock cycle in simulation starts, all processes are executed that are sensitive to the clock edge. These processes might produce new events by changing the values of their outports who then change the values of the connected inports. These events are stored in a last in, first out queue (LIFO). Once all processes have been called SystemC checks the LIFO for events that would trigger new processes and starts to execute these, memorising again all newly triggered events. These iterations are called delta cycles and a clock cycle in simulation is usually split into

multiple delta cycles. The simulation for the current clock cycle ends, when the list of new events is empty at the end of a delta cycle [2].

#### 2.2 MicroLib

MicroLib [5] has been introduced as an effort to build a library of processor simulator components. It focuses strongly on a modular approach to simulation. It can be seen as an advancement of the idea provided by the SystemC simulation environment. In fact most modules for MicroLib have been developed using SystemC. But in SystemC the huge freedom has led to a situation where every research group has developed their own modules. These modules contain often completely different interfaces and because of this they are mostly incompatible with each other. One of MicroLibs efforts is to introduce common interface standard such that modules will become compatible even when developed by different groups. The idea is that researchers should be able to easily download these modules in order to reuse them for their purpose. They should be able to connect them at their will and add their own modules. But they should be able to do this without having to further study the behavior of the SystemC ports interfacing these modules. Reuse should become as easy as plugging together a computer workstation: Components that are supposed to fit do so, others not. In fact MicroLib provides already a set of components including processors [22, 15] and a big library of caches [46]. These modules can be arbitrarily branched together as long as their connection makes any sense.

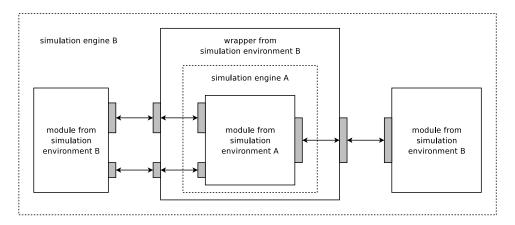

A major difference to past developments is that MicroLib is not trying to compete with other existing modular environments like Liberty. Instead its goal is to introduce wrappers that will allow it to connect modules from different simulation environments. A wrapper for SimpleScalar has already been introduced and as I will present in section 5.2 a Liberty wrapper that is currently being worked on. By this MicroLib is trying to build the largest possible library of component modules for processor simulation.

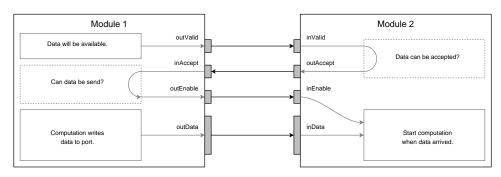

Figure 2: Handshaking protocol introduced by MicroLib.

In order to increase compatibility MicroLib has introduced a handshaking protocol to pass values between modules. This handshaking is always done for groups of ports that are supposed to process coherent data. Such ports might be the data, address and command ports going from the CPU to the cache. It is evident that the cache cannot process the query unless all three values are known, thus they can be seen as a group. Each such group gets a set of three control lines assigned to them, namely valid, acknowledge, and enable. While valid and enable connect the sending module to the receiving module, acknowledge connects the receiving module to the sending module. The functions of the handshaking signals are as follows. Valid serves to notify the receiving module that valid data will or will not be available by sending true or false. The receiver uses acknowledge to communicate to the sender if he can process the data. Finally the sender has to write the data to the corresponding ports and set enable to true to indicate that the data is available. In fact, we will see a very similar handshaking protocol later on in Liberty (Section 2.3). I have implemented all my modules such that they use this handshaking protocol. Figure 2 shows a schema of this protocol. The following code is an example of how the protocol implementation for one group of ports could look like:

DataTreater(const sc\_module\_name& name) : sc\_module(name) { . . . SC\_METHOD(ForwardValid); sensitive << inValid;</pre> SC\_METHOD(ForwardEnable); sensitive << inEnable; SC\_METHOD(ForwardAccept); sensitive << inAccept; } void ForwardValid() { if (inEnable) { // data arrived, threat it. } // forward the signal outValid = inEnable; // Forwards and broadcast accept signal.

```

void ForwardAccept() {

// Accept all incoming data.

outAccept = inValid;

}

// Forwards enable signals.

void ForwardEnable() {

// Allways send data when accepted outEnable = inAccept;

}

```

Another tool so far distributed on MicroLib is FastSysC [2], a fast SystemC simulation engine. Since I have used it to speed up my simulations I have added a short description to the end of this report. It is available in appendix A.

# 2.3 Liberty

When speaking about Liberty most frequently the Liberty Simulation Environment (LSE) [13] is meant. While similar to SystemC and MicroLib in its overall structure, LSE does still differ. In LSE models are also constructed modular in a manner parallel to that of real hardware structures. LSE specifications, that are compiled into simulators, are a collection of connected modules that are instantiated from templates. This templates are called modules. There are two types of modules: leaf modules and hierarchical modules. The behavior of leaf modules is specified by sequential code that uses the LSE API to compute, send and receive data. On the contrary hierarchical modules are composed of a collection of interconnected leaf modules. These hierarchical modules can still contain special build algorithms allowing for an enormous flexibility. Thus, LSE provides low overhead component based reuse [13].

A major difference to other simulation system is, that LSE model specifications can be compiled, since the structure of the model is known at compile time. Thus optimizations like those done by the FastSysC schedule generator<sup>2</sup> can be easily performet by the LSE compiler. In addition the compiler can remove unused signals and optimize code where needed. For example even when FastSysC genereates a static schedule every component still has its own processes which needs to be called during most simulation cycles. Such calls generate computation overhead due to access to the stack. The

<sup>&</sup>lt;sup>2</sup>Please see appendix A for details.

Liberty compiler can actually generate sequential code. When this code is finally compiled by gcc it can run much more efficient than that written by the user when working with SystemC.

Liberty modules are defined in Liberty Structural Specification (LSS) files. Like in SystemC they contain inports and outports in arbitrary numbers. Unlike in SystemC where each port can be of any type, even a class type, LSE supports only very basic types like integers, characters, strings, arrays and structs. This is due to an otherwise very usefull feature in Liberty. This feature is the support for polymorphism that is not provided in this manner by SystemC. In Liberty data types for ports and other entities can be declared to be polymorphic (i.e. to have many types). Utilization is very convenient since LSE tries to determine the appropriate type for polymorphic ports and variables automatically when possible [13]. This futher facilitates module reuse.

To specify component behavior or allow for later parametrization user-points are used. These are variables that contain algorithms called on special events. There are userpoints for module initialization, userpoints for when data arrives on a port or simply user defined userpoints that are called according to module specification. During compilation LSE simply inserts the code contained in userpoints in the appropriate places.

The distribution of LSE contains already a component library of standard components like queues, routers, arbiters, control modules, and other utility modules. These components can be easily reconfigured using userpoints to create most common modules. To use these modules the library has to be included using the command using corelib. For example in order to create a xor gate a combiner module can be used. The combiner module is a flexible module whose instances can be parametrized to compute an arbitrary number of outputs from an arbitrary number of inputs. The userpoint combine contains the code that computes the result. The LSS code of the xor gate looks like this:

```

module xor_gate {

using corelib;

inport in0:boolean;

inport in1:boolean;

outport out:boolean;

instance gate:combiner;

gate.inputs={"in0","in1"};

gate.outputs={"out"};

gate.combine = <<< *out_id=in0_id;</pre>

```

To connect two ports in LSE no special signal object is required. Instead the user simply writes module1.outport ->[type] module2.inport. The type is optional and can server for type resolution during compilation when there is no other mean of determining a connection type. This can happen when data is circularly passed between polymorphic modules.

Another difference in regard to SystemC is, that LSE handles timing quite different. Instead of providing clocks, LSE propagates stall signals. A special control signal structure is used for that, similar to that described in Section 2.2 regarding MicroLib. In addition to the data a port contains three control lines, namely if the data is valid, an acknowledge signal, and an enable signal. At the beginning of a cycle all control lines are set to unknown. In the same manner as described above for FastSysC the singal lines are used in LSE. Valid signals to the receiver whether or not data is going to be available. The receiver signals the sender via acknowledge if he can accept the data. Final the sender writes the data to the port and signals the receiver using the enable signal.

LSE also offers a far more advanced way of data monitoring and logging than SystemC. In SystemC the user monitored actions by placing ifstatements and printf calls all over the module code. LSE provides special collector objects for this. They are defined using the keyword collector. The eventname to be monitored and the name of the monitored module are given as parameters. After that actions to be taken when the monitored event takes place can be defined. Again during compilation LSE can choose the best possible placement for the code in the final simulator.

With these tools the LFSR from figure 1 can already be constructed. Parts of the code follow. Please not that we only needed to redefine the xor gate. The other modules like flipflop (delay) and the tee are taken directly from the Liberty corelib:

```

using corelib;

include "xor_gate.lss";

instance bit0 : delay;

instance bit1 : delay;

instance bit2 : delay;

instance xor : xor_gate;

```

```

instance bit1_tee : tee;

bit0.initial_state = <<< *init_id = LSE_dynid_create();</pre>

*init_value = TRUE;

return TRUE; >>>;

. . .

bit2.out -> bit1.in;

bit1.out -> bit1_tee.in;

bit1_tee.out[0] -> xor.in0;

bit1_tee.out[1] -> bit0.in;

bit0.out -> xor.in1;

xor.out -> bit2.in;

collector STORED_DATA on "bit2" {

. . .

record=<<<

printf(LSE_time_print_args(LSE_time_now));

printf(": bit2=%d\n", *datap);

>>>;

};

```

Again the full code of the LFSR can be found in Appendix D.

### 2.4 SimpleScalar

SimpleScalar [14] is a suit of simulation tools that offer low detail and high detail simulation of microprocessors. These levels range from a high-performance functional simulator to detailed models of superscalar processors including caches, speculative execution and branch prediction. In difference to SystemC and Liberty SimpleScalar is not modular. It is designed to simulate processors and a part of their environment, not more. Because of this SimpleScalar is well optimized and has been widely used in processor simulation [39, 45]. SimpleScalar is also available as source code. It has been initially developed to support a MIPS derived instruction set architecture (ISA) called PISA. Later versions have added support for architectures such as Alpha, ARM, PowerPC, and x86. Thus it really is not one simulator but contains multiple simulation and emulation programs. The most used

of these simulators is sim-outorder that lets the user simulate out-of-order<sup>3</sup> processors.

# 3 Design choices

The goal was to create a library that would allow to construct a running CMP simulator. In order to do so I needed to implement a set of components that every CMP system needs. These components are clearly at least a processor core, caches and memories, and the substantial interconnect. Especially the interconnect needs to be chosen with care since it dominates the overall architecture of the CMP. In the following I will present different existing CMPs and their interconnection networks as well as some stand-alone interconnect solutions. I will evaluate these approaches and excerpt from them different possibilities for the desired modules. Finally I will present and explain my choices.

# 3.1 Existing CMP architectures and interconnects

I will start by presenting three existing Chip Multiprocessors and their different interconnection architectures. The first two, the Stanford Hydra CMP and the MIT RAW Microprocessor, are research projects. The Stanford Hyrda CMP implements a shared bus architecture. A completely different approach is presented by the MIT RAW Processor that implements multiple packet-switched networks. The third solution presented, the Cell Processor, is a commercial product that is currently in development. Its interconnect is a mergence of the first two solutions. After having presented the CMP solutions and their networks I will describe two further interconnection architectures. One is an interconnect called crossbar and the other is an all-round implementation of a packet-switched network on chip called SPIN.

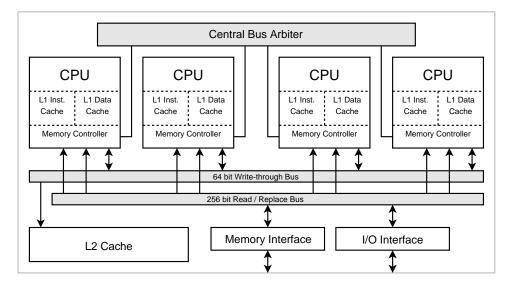

#### 3.1.1 A shared bus solution: Stanford Hydra CMP

The Stanford Hydra Chip Multiprocessor [12] contains four MIPS <sup>4</sup> based cores. Each of the cores contains its own primary instruction and data caches. The Hydra cores are in-order processors. They are connected to a single shared second level cache via two *shared buses*: one 256 bits wide bus

<sup>&</sup>lt;sup>3</sup>Out-of-order means that the processor rearranges instructions in regard to the constraints given by dependencies. This allows to execute further instructions when only a part of the processor is stalled by the current instruction. Out-of-order execution is widely used in today's superscalar processors. In contrast in-order processors execute instructions in the same order as they arrive from memory. These processors are slower but usually consume much less die area.

<sup>&</sup>lt;sup>4</sup>MIPS stand for Machine without Interlocked PipeStages. It is a Reduced Instruction Set Computer (RISC) architecture developed 1981 at Stanford University that is being used in processors worldwide until today.

for read operations and one 64 bits wide bus for write-through operations. Both buses are pipelined in order to maintain a high clock frequency. Thanks to this data can enter and leave each bus on every clock cycle.

Figure 3: Architecture of the Hydra CMP without the speculative support.

The read bus was designed to handle an entire cache line in one clock cycle. It thus allows for a very fast communication between processors, secondary cache and off-chip memory. The write-through bus communicates all writes made by the four cores directly to the second level cache. It also broadcasts the write to other processors, eventually invalidating corresponding cache lines in their primary caches. Thus it helps to maintain coherent level one caches. The general Hydra architecture can be seen in figure 3.

Hydras shared bus solution allows for a latency of 10 to 20 cycles for interprocessor communication. Unfortunately it does not scale well beyond 8 processors as its creators have admitted themselves [12]. It is clear that a single bus cannot cope with an arbitrarily increasing number of processors. Even if we increase the bandwidth of the bus it has no ability to respond to multiple requests at a time. Thus with the number of processors the latency for memory requests grows. The authors of the Hydra CMP propose to use either more buses, a crossbar interconnection or a hierarchy of connections to account for this problem. Some of these suggestions I will discus in the following sections.

The Hydra CMP implements what is called *thread-level speculation*. This method tries to exploit *instruction level parallelism (ILP)* in sequential uniprocessor programs. To do so the Hydra CMP arbitrary splits a program code sequence into a sequenced group of threads that can be executed in parallel on different cores. The Hydra CMP contains special hardware that ensures

that no data dependencies <sup>5</sup> between threads are violated. In the case that a thread from the sequence causes a true dependency violation the Hydra will re-execute this sequence with the correct data once this data is available.

The performance of the Hydra CMP is given as speedup compared to the execution time of the same code on one Hydra core. While in fact the Hydra CMP with its four cores does extract quite high speed up this needs to be seen with careful consideration since a single Hydra Core is far less powerful than a superscalar processor taking the same area of the die chip as four Hydra cores.

#### 3.1.2 Packet-switched networks: MIT RAW Microprocessor

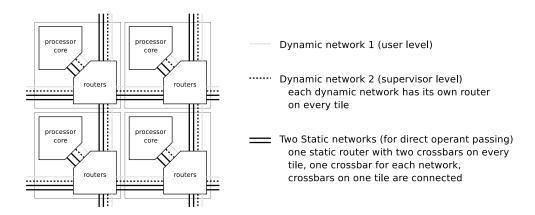

Figure 4: A schematic 2x2 grid of RAW tiles.

The MIT RAW Microprocessor [9] is another example of a chip multiprocessor. It is also implemented using MIPS based cores. In contrast to the Hydra CMP that used a shared bus the RAW microprocessor implements several networks on its chip to connect its cores. The chip is segmented into quadratic tiles that each contain a processor, a level one data cache, a software managed level one program cache, and programmable routers. The routers implement nodes of the network that control the data flow. They are interconnected via links and form three global on chip networks. The schema of this network can be seen in figure 4. Each Tile contains three routers: two dynamic routers and one static. Routers of one network are connected to routers of the same network on neighboring tiles via a full duplex 32 bit link. In the case of the static routers two such links are used between two neighboring tiles.

<sup>&</sup>lt;sup>5</sup>The possible dependencies are: read after write (RAW), write after read (WAR), and write after write (WAW). The exact algorithm by which Hydra handles these dependencies is not of importance to this project and is thus not further explained. It can be seen in detail in [12].

The two dynamic networks are packet-switched and implement wormhole-routing. Packet-switched means that data is divided into several smaller chunks called packets that are send over the network. This is done instead of sending the data in a continuous stream. While a continuous stream guaranties bandwidth it completely blocks a part of the network for other users. This is only reasonable if high-bandwidth applications are used. Packet-switched networks on the contrary do not guaranty bandwidth but allow multiple users to take advantage of one connection simultaneously.

Wormhole-routing means that instead of waiting until the whole packet arrives the router only waits for the packet header and then forwards it already to the next node in the network. This way packets worm their way through the network. Unfortunately in a wormhole-routed network congestion might occur. This can happen when to many messages are fed into the network and the buffers of the routers fill up. In this case a network will simply stop to accept new messages and not deliver the ones pending. Thus this phenomenon is also called deadlock.

There are two solutions for this problem. The first one is called deadlock prevention. It allows every network user to send only a certain amount of messages at a time based on a credit system. While this solution prevents congestion it limits network performance. The second solution is called deadlock recovery. In this case there is special hardware to detect network congestion. When this happens the network contents are partially flushed to a temporary buffer in order to allow for recovery. While this solution does not limit performance it necessitates an additional framework to move the data out of the network.

The RAW Microprocessor implements both types of networks. One of the dynamic networks is dedicated to trusted users, like the operating system, data caches and DMA controllers. This network uses the *deadlock prevention* technique. The other dynamic network can be used by programs to pass messages. It implements *deadlock recovery*. When congestion occurs the contents of the network are flushed to external buffers using the first dynamic network.

The third and static network has a quite different purpose. It is used directly by the hardware to pass operands between the compute pipelines of different cores. In order to be efficient this network is directly connected to the pipeline. In fact when the program writes to register 25 through 28 the value is not stores in the register file but send to the static network. When reading from these registers the processors reads from the incoming static network buffers. If these buffers are empty the processor stalls and waits until data arrives. The output is buffered as well and when buffers are full the pipeline will stall as well.

In order to control the network each tile contains two dynamic routers and static router. Each router is connect to one of the three networks. While the dynamic routers switch the packets according to the packet header the static

router is run by a program. It fetches its instructions from the corresponding level one instruction cache. These instructions contain routes for both of the static routers crossbars. Crossbars are the hardware structures that create connections between the incoming and the outgoing network links. They are further explained in section 3.1.4. The crossbars are connected to the four links of the four neighboring tiles, the processor, the router pipeline and to each other. A static router instruction sets the connections of the crossbars and instructs the router pipeline in order to implement simple loops and conditions for the static router program. This architecture allows the RAW Microprocessor to pass values between two computing cores with a latency of only 2 + X + 1 + Y + 2 cycles where X and Y are the number of tiles the signal has to travel horizontally and vertically. Two cycles are needed to introduce the signal into the network, X cycles for the horizontal tiles, one cycle for the turn, Y cycles for the vertical tiles, and finally two cycles for the singal to reenter the destination pipeline. The one cycle latency for the turn is due to optimizations to the wires that exploit the fact that they mainly run straight between the tiles.

Figure 4 displays a grid of only 2x2 tiles. It is evident that this structure is scalable in the number of tiles. The RAW Chip is implemented with 16 tiles but multiple chips are branched together to form larger structures. Performance of the RAW Chip is also measured in speedup compared to a single RAW tile. The Results show also an impressive speedup in certain applications. Like in Hydra this speedup is very dependant on the ILP present in the program executed.

A critical point not mentioned in any RAW paper I have found is actual network saturation when the grid grows bigger. Since memories are connected to the outside of the raw grid (as on all processor dies) the inner tiles of the grid are further away from them. The RAW team has failed to investigate the effect of larger grids then just 16 processors. Most likely in the case of a huge grid the inner cores will experience very fast rising memory access latency in applications that require high bandwidth. This is a very important point that should be yet considered.

#### 3.1.3 A ring bus: Cell Processor

The Cell Microprocessor [44, 42, 43, 26] is being developed in cooperation by Sony, Toshiba, and IBM. Unlike the first two processors described this is a commercial product that is intended to be used in Sony's Playstation 3. Due to this fact there is only little detailed information publicly available. Thus I was not able to find more reliable sources than the three mentioned above except for magazine articles. Due to this secrecy the Cell processor is *not* suited for serving as a main model for our modules. It would be almost impossible to implement it realistically enough due to a lot of missing information on architectural details. Since it implements a different approach

and confirms some general trends in CMPs I felt that the Cell Processor was still worth mentioning.

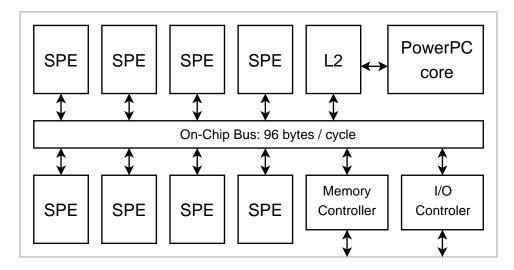

Figure 5: High-level organization of the Cell Processor.

The Cell processor implements a non homogeneous CMP. Figure 5 displays its general structure. It contains one master CPU and eight slave cores. The master CPU is a 64 bit dual threaded Simultaneous Multithreading (SMT) PowerPC core. SMT means that multiple threads are executed in parallel on a machine in order to exploit ILP. In the case of the Cell Processors master CPU two in-order pipelines allow for the execution of two threads in parallel. This core is equipped with primary 32 KB instruction and data caches and a 512 KB level two cache.

The eight smaller cores are called  $Synergistic\ Processor\ Elements\ (SPE)$ . These cores are dual issue  $SIMD^6$  processors. This is why they are sometimes also called  $SIMD\ Processor\ Elements\ (SPE)$ . A new ISA has been defined in order to allow for addressing of a 128 entry register file. Each entry is 128 bits wide. Thus each of the two threads of a SPE is capable of operating on four 32 bit values in parallel. Each SPE has a local 256 KB static RAM. The SPEs abstain from the use of a cache hierarchy. Instead the master CPU can instruct them to copy a certain location of main memory via  $DMA^7$  into its local SRAM. In the same manner the master CPU can later instruct the SPEs to copy the data back again.

All SPEs as well as the master CPU are connected to memory and I/O

<sup>&</sup>lt;sup>6</sup>Single Instruction Multiple Data: This means that one instruction of the processor operates on multiple values of data in parallel.

<sup>&</sup>lt;sup>7</sup>Direct Memory Access: A method were not software but a special hardware resource manages the transfer of data blocks from one memory address to another or to a completely different memory component as in the case of the Cell Processor.

via a high performance bus called Element Interface Bus (EIB). It consists of 4 unidirectional data rings, two in one direction and two in the other. The rings run at half the processor frequency and transport a total of up to 96 bytes per cycle. Each ring supports up to three simultaneously transfers when these are done between neighboring nodes. Thus the EIB hardware does more resemble a network than a real bus.

#### 3.1.4 A crossbar interconnect

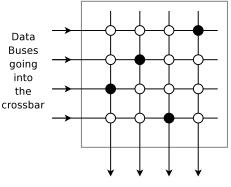

A crossbar can be seen in Figure 6. In general a crossbar connects n components on one side with m components on the other side. The particularity of a crossbar is, that it allows for multiple parallel connections if these are independent. Let us take for example a crossbar that connects eight CPU cores to four secondary cache banks. In this case any four of the processors can access the level two cache in parallel as long as they each access a different cache bank. In order to allow for this the crossbar needs four internal buses. Each cache bank is connected with exactly on of these buses (and each with a different). Opposite to this each CPU core is connected to all four buses. When any of the cores makes a request to access one of the cache banks it will be connected to the appropriate bus given that this bus is not currently in use. An internal arbiter controls accesses and eventually puts a CPU core on wait if two or more cores try to access the same cache bank in parallel. Crossbars are not only used for huge buses. In each of the routers as used by the RAW Microprocessor a crossbar is used. The static router even uses two.

However it is evident that a crossbar scales by the square of the number

Data Buses leaving the crossbar

Figure 6: A 4x4 crossbar. Data arriving on the inports of the crossbar (left) can be routed in an arbitrary manner to the outports (bottom) by setting the appropriate connections (dark dots).

of components connected to it. In the example above we needed four buses and 32 connections to these. Thus I have found no implementations using a crossbar as a chip interconnect with more than eight processors attached. A recent research effort [36] modeled such a crossbar connecting eight cores with a shared level two cache. It confirms the huge area overhead generated by a crossbar interconnect. It has to be mentioned though that in this paper area overhead was also very dependant on the mechanism of cache sharing. Thus the results are hard to interpret regarding a simple crossbar that connects for example only processors.

#### 3.1.5 SPIN

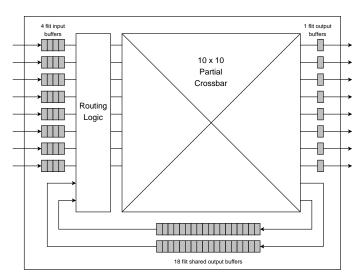

SPIN stands for Scalable Programmable Integrated Network. While the RAW networks are adapted to the processors needs, SPIN has been designed to serve as an interconnect for systems on chip (SoC) in general [8]. SPIN is a packet switching network that consists of routers as the network nodes and bidirectional point to point links as connections. Additional wrappers server as an interface to the network that allows clients to send and receive messages. These wrappers translate address space requests into packets with the according node address and inject them into the network. When the packets arrives at its destination a wrapper re-translates it into an address space request. The packets send over the network are split into 32bit pieces that are called flits (flow control units). Each packet contains a header flit with the destination address and packet type and size. The packets are terminated by a control flit that contains a check sum (CRC). The packets are wormholed through the network by the routers.

Figure 7: RSPIN: The router for the SPIN network.

A router for SPIN, called RSPIN, can be seen in figure 7. It has eight ingoing and eight outgoing connections (network links). The ingoing connections contain buffers for up to four flits each and the outgoing connections contain a buffer for one flit each. In addition each RSPIN contains two 18 flit output buffers that are shared by all incoming connections. These buffers have greater priority when competing with the input buffers for an output link. This allows to reduce contention [7]. The central component of the RSPIN is a 10 x 10 partial crossbar. This crossbar is only partial since it is designed for a special network topology and only certain connections between links are possible.

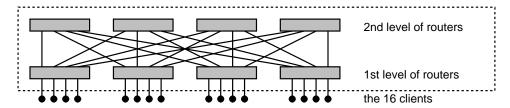

Figure 8: The FAT tree topology of SPIN.

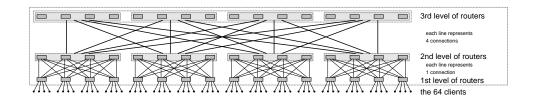

The topology that has been chosen by the SPIN designers is called a fat tree. This is a tree structure with routers on the nodes and terminals on the leaves of the network graph. In a fat tree each node can contain multiple fathers and guarantees enough bandwidth to the higher level for all of its children. An example of a fat-tree topology with 16 clients (leaves) can be seen in figure 8. Another fat-tree can be seen in figure 9. It is evident that fat-tree topologies are scalable.

For evaluation the network has been compared to a PI<sup>8</sup> bus. In the test between four and 32 cores were used and delivery time was measured to deliver all messages in a pooling. Pooling means that each client sends messages to all other clients. Another measurement was the latency of messages when varying overall network load. Results showed that SPIN beats the PI bus in latency time when at least 16 clients were used. It is important to note that this result was only received when SPIN used a special split protocol allowing it to send a second request (message) before the first one was answered by the target. If this protocol was not used SPIN produced higher latencies than the PI bus even with 32 clients. In the saturation test SPIN offered a lot more possible load by saturating for an offered load of 28% of the maximum possible load. The PI bus saturated already with an offered load of 4%.

<sup>&</sup>lt;sup>8</sup>Peripheral Interface

Figure 9: A 3 level fat-tree topology. The thick connection lines connect each router from a group of four with the correspondint router from a second group of four routers.

# 3.2 Selecting a Network on Chip for CMP

When selecting an interconnection network I was in particular looking for a solution that would scale well beyond hundreds of processors. As possible candidates I have considered the interconnects presented above. They were:

- A shared bus system like in the Hydra CMP.

- A virtual shared bus system that is implemented using a small network (four rings) as in the Cell processor.

- Statically or dynamically routed networks, like in the RAW Microprocessor or SPIN.

- A crossbar interconnect.

As I have mentioned in section 3.1.1 when talking about Hydra the shared bus system suffers from lack of scalability. A recent research effort has further examined this problem by connecting 4, 8, and 16 cores via a shared bus. The percentual performance decrease due to connection overhead grew with the number of processors [36]. The same was true for a crossbar and when looking at current solutions it is clear that a crossbar for a hundred processors is virtually impossible.

There is still another problem encountered with the interconnection architectures just mentioned. As well the shared bus as the crossbar suffer from a common disease: they rely on a global control of the information traffic. But this method is limited in scalability due to the fact that the interconnect needs to know each components state [28]. Thus neither a shared bus solution nor a crossbar seemed to suit the requirements for a highly scalable interconnection component.

The Cell Processor has solved the connection issue by implementing a virtual bus that consists really of a small network on chip. This solution is similar to SPIN where a complete network on chip is virtually hidden to the clients by introducing wrappers that translate address space requests into

packets. RAWs solution differs in the fact that the clients actually see the network. They are responsible themselves to correctly address packages and for their coherency.

While all these network based approaches have not really been tested beyond a handfull of processors they seems to be much more promising than a simple hardware bus or crossbar. The RAW processor actually succeeded in connecting the most cores. And even though I doubt that RAWs architecture will flawlessly allow to connect hundreds of corres with its current topology further research might find new network topologies that solve this problem. Considering that three of the solutions proposed were based on a network (RAW, Cell, SPIN) I have decided to implement a packet-switched network module. I have tried to keep the module as general as possible only hardcoding the most necessary structures for packet-switching. This way I have left the freedom to the user of the module to actually implement the details by setting parameters and adding code.

# 3.3 Selecting a core for CMP

Above I have presented three existing Chip Multiprocessors. The first two, the Stanford Hydra CMP and the MIT RAW Microprocessor, are research projects. The third processor presented, the Cell Processor, is a commercial product that is currently in development. While there are other CMPs I believe these processors cover a wide range of possibilities. In fact the Hydra CMP and the RAW Microprocessor are the most referenced CMPs found in research papers. The Cell Processor seems to be the first high-performance general-purpose commercial product that implements as many as 9 separate cores on a single chip. Since I was looking for structures that would scale to huge numbers of processors I have not investigated further CMPs like the IBM Power 4 which implements two superscalar cores on a single chip [31, 41].

When looking at the three cores presented several similarities stand out:

- All cores have some type of local instruction and data storage. These are either level one caches or simple SRAM.

- Each of the CMPs uses in-order execution in their cores. Even the master CPU of the Cell Processor is in-order.

- The cores are all held simple executing RISC code. In fact the Cell Processor is even the only one using SMT. All other cores are strict single-issue processors.

- The Cell Processor is the only one even having a special master CPU. The other architectures are completely homogeneous and the master is chosen in software by the operating system for example.

The first point is quite logical and inherited from the single processor. In order to allow for fast execution the instructions and data worked on have to be as close to the compute elements as possible. This is required to reduce latency due to wire delay. Thus the implementation of level one caches for instructions and data is essential even in the most simple cores in order to have an efficient execution.

The second and third point results from the fact that the consumend area of the processor increases drastically with its complexity. As noticed in [40] the gain from more cores due to saved space is higher than the loss due to in-order execution. Thus I have decided to implement a simple core that was designed for resuse. Because of this the use of existing models like PowerPC750, OoOSysC or even SimpleScalar [15, 22, 14] as cores was not an option.

The forth point did not change anything in the choice of the core. It is worth mentioning that my implementation does well support such a master. One can easily branch more complex processor modules like the PowerPC750 or OoOSysC to a constructed simulation network with lots of basic cores.

Further points to consider were the *instruction set architecture* (ISA) and that the processor be not out of date. I considered the MIPS and the PowerPC ISA since they have been used in the existing solutions. Also both are very widespread and supported by gcc, a very important point when choosing the ISA since researchers need to be able to compile test programs.

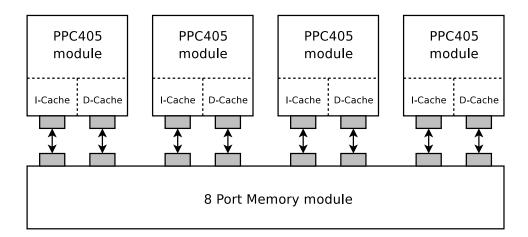

I finally decided for the *PowerPC* version since our team had already experience with it and since we had a valid *PowerPC* emulator to verify my results. As a concrete processor I chose the *PowerPC* 405. My choice was motivated by the fact that it is a PowerPC core specially designed for the use in systems on chip [18]. It implements a 5 state in-order pipeline and contains separate instruction and data primary caches. This suited perfectly the requirements for local storage in each core. The PowerPC 405 is commonly used on the market segment an still being supported [31, 30]. Because of that it is relatively well documented [17, 18]. Thus the PowerPC 405 suited all the requirements.

# 3.4 Selecting a memory

A last decision I made and which needs no further discussion, is to implement a memory module. This module could serve as the central memory or be used locally for each processor core. Again I have tried to make it as flexible as possible by allowing the memory to have as many ports as desired and to adjust timing.

<sup>&</sup>lt;sup>9</sup>Architectural details of commercial processors are often kept secret by the companies. With relatively I mean that human-readable information is available that is far more detailed than that available on some other processors. Please refer to section 4.1.1.

# 4 Implementation of the modules

This section describes architectural details about the three modules implemented. These modules are a PowerPC 405 module, a network on chip (NoC) module, and a memory module as decided in the previous section.

# 4.1 The PowerPC 405 processor module

Developement and coding of the PowerPC 405 processor module required by far the most time. Thus I will start by naming some common problems encountered when working on the PowerPC 405 module. Next I will give an introducing the hardware architecture of the PowerPC 405 chip followed by some key facts about the PowerPC 405 ISA. The final part concerns the actual implementation of the module for SystemC. It talks also about how I tried to improve simulation speed.

#### 4.1.1 Problems encountered

The following list names only a few difficulties encountered when implementing a processor:

- The manuals and white papers often contain only sketchy information that mostly creates more new questions than it answers.

- Processors often split incoming instructions into multiple microinstructions. This behavior is left completely undocumented and the developer has to make guesses based on bits of information gathered from the most unlikely places of the manual or from the web community.

- Choices made regarding implementation techniques can later on create new problems. Using the host system to execute system calls for example creates the need to have direct accesse into simulated memory instead of using the simulated datapaths.

- Debugging is very time consuming due to the complexity of the structured model. It can be shortened by generating a lot of output during execution. But even then the error has to be found in this output.

- Finally in order to test and debug certain parts of the module each time new testing code has to be written and compiled. In special cases this includes time-killing coding in assembler.

I felt that these problems are worth mentioning since they are specific to this domain and do not just result from typical problems encountered during code development. The research team I have been working with has confirmed to me that the mentioned issues are mostly unavoidable. Some are also mentioned in [5]. There is no real solution to these matters. I have tried to make my code as readable and documented as possible in order to facilitate debugging and reuse by others. When a *verbose* variable is set the simulator will print almost every of its actions on the screen in detail allowing again for better debugging. This has helped me save a lot of hours during development I believe. Unfortunately the problem mentioned concerning the documentation has cost me a lot of time. It happend to me multiple times that I had implemented a feature into the processor and have later found more detailed information that made me change the implementation. The reason for this was not that I have not searched exhaustively enough, but that this information is given on completely unexpected placed.

#### 4.1.2 Hardware architecture

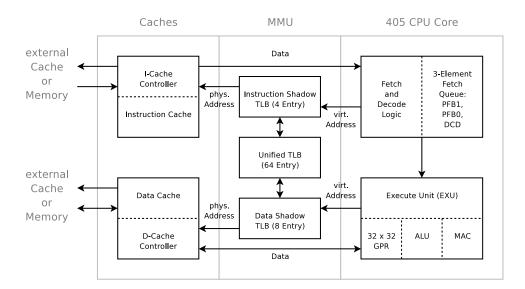

Figure 10 shows the PowerPC 405 block diagram. The PowerPC 405 consists of three parts: the *CPU*, the *MMU* and the *caches*. There are two separate caches, one for instructions and one for data.

Please note that the MMU can be simply left away. Since I am only executing user code at the moment this is what I did in order to save development time and increase simulation speed. This is also why I am not going to further investigate its functions in this report. For future implementations the MMU can be added relatively fast since the code is structured in a very clear manner in the area where CPU and caches interact. The same is true

Figure 10: PowerPC 405 CPU core block diagram. Note that the MMU can be switched of in the PowerPC 405. Since we are momentarily only executing user code we simply left out the MMU in our first implementation.

for the processors handling of exceptions. Since I run test programs only in user mode and suppose them to be correct no exceptions need to be handled. I have thus not implemented the exception handling in the simulator.

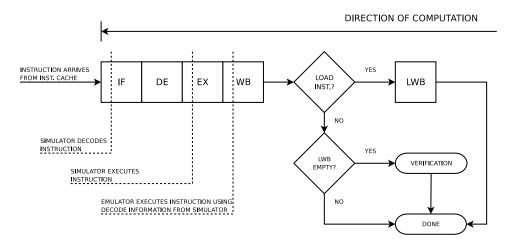

The CPU contains five pipeline stages. They are: instruction fetch (IF), instruction decode (ID), execute (EX), register write-back (WB), and load write-back (LWB). These stages are implemented by two units: the instruction fetch unit and the execute unit.

The instruction fetch unit containts the instruction fetcher. It implements a three stage instruction queue with its elements in the following order: prefetch buffer 1 (PFB1), prefetch buffer 0 (PFB0), decode (DCD). Instructions are fetched two at a time along the predicted path. Branch prediction is done in DCD and PFB0. If for example a branch instruction in PFB0 is predicted taken than the predicted path is fetched into PFB1. PFB1 is flushed before if it already contained the next instruction. When the instruction queue is empty instructions are fetched directly into the DCD buffer. The Instruction contained in DCD is decoded during the ID stage. It can then pass into the Execute stage next cycle. All instructions must pass through DCD before entering the execute unit.

The execute unit (EXU) contains the arithmetic logic unit (ALU), the multiply-accumulate unit (MAC), and the register file (RF). It is a singe issue unit, meaning that it can only start executing one instruction at a time. Instructions are executed in-order with an exception being load instructions. These can wait for the data to arrive from memory while following instructions continue execution given that they are independent of the load result. All results except for load results are written into the register file during the write-back stage. The results of load instructions are written back during the load write-back stage in witch those instructions also wait for the data to arrive from memory. Thus all but load instructions retire in the write-back stage and load instructions retire in the load write-back stage. This has an important effect when using an emulator for simulator verification. Please refer to Section 4.1.5 for details.

Internally the PowerPC 405 core architecture is big endian but it supports both little endian and big endian data format. This further increases compatibility with other hardware blocks being placed on the same chip or externally. In order to provide this feature the instruction set contains reverse order load/store instructions. In addition the instruction cache rearranges instructions stored in little endian format before storing them in the cache array.

The instruction cache is read only. It is connected by an unidirectional eight byte bus to the fetcher. The data cache is connected to the execute unit using a bidirectional eight byte bus. The bus allows the cache to simultaneously accept a new request and answer an outstanding one. The widths of the buses allow for fetching two instructions at a time and writing and reading two registers at a time for certain multiple load/store instructions.

Both caches are two-way-associative with a line width of 32 bytes. The total number of cache lines depends on the size of the cache<sup>10</sup>. Since the caches are independent they can be of different size. Both caches have 32 byte line fill buffers. These buffers allow for further cache requests to be served if they are cache hits during an on-going line fill. For non-cacheable line accesses both caches utilize the line fill buffer even thought the line is not going to be written into the cache array. The data read stays in the buffers until it is overwritten by a subsequent memory request. This way subsequent non-cacheable request can be served a lot faster since they do not need to load the corresponding line multiple times.